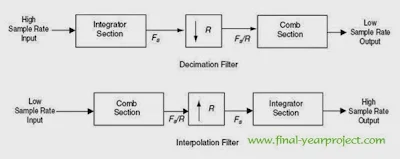

The CIC filter can implement an interpolation or decimation filter (see above fig.) that uses only delay and add operations and thus is well-suited for FPGA and ASIC implementation. Furthermore, the same basic filter structure can be used to handle variable sample rate conversion.

The major blocks in design would include digital I and Q carrier generators, digital mixers, decimating/interpolating CIC filters and clock distribution circuits. The blocks such as, adder, multipliers, registers and clock & control circuitry will be used in implementing these blocks.

Recommended Project: RISC Processor using the Verilog Hardware Description Language (VHDL)

In this paper, OUI is used which is SOPC builder provides to design the hardware of CIC decimation filter component. We design the software driver files for the hardware of CIC component, generate a component and establish an SOPC system in SOPC Builder. Finally, the designed system is downloaded to the device and verified in FPGA.

Author:- Ripudaman Singh Rathore and Rajat Arora

Download

Advertisements:-

![[2025] In-Demand Final Year Projects for Computer Science](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEiPLaQX8S831tmthK7PFgJ6KJQdDJWs5NsY3QREotosR7GUpFsyaw7w80Lrt2nBuz-02KsN5TxtaYtF21u7HLSKFQPxyncmbrOWF3n3DQNiEKCjFb9p4I4-3yYoxKKijLL0lNqaHeCMK1VmZSwEFP2e4esMfpyqMv6iBv6bSe4ZsmmKkOTYEgD47RFYDjE7/s72-c/In-Demand%20Final%20Year%20Projects%20for%20Computer%20Science.jpg)

![Final Year Projects for CSE [2025]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEicwsr89FawhHP1j_XcxTGTU5DxuevpZUQTgFlo_rzjh2YOVGC68ii16T6I7pLcUrR9mu9pVkGsEe_eXBWZhf3fBL-MyLFmw8l0BhRYNOEchX5TlIPCvHoiED-Ix_ZpIbH7T7bklprg5YlabbOX6fPz1Y5-Q4TF7i-MLIEAfbaSjvsJmbnTr91t8i_7Ag/s72-c/final%20year%20projects%20for%20cse.png)

No comments:

Post a Comment